서버 | 차세대 인텔 제온 스케일러블 프로세서, 사파이어 래피즈(Sapphire Rapids)

인텔 아키텍처 데이 2021(Intel Architecture Day 2021)을 8월 19일(현지시간) 개최하고 차세대 제온 스케일러블 프로세서인 사파이어 래피즈(Sapphire Rapids)와 인텔 인프라 처리 장치(IPU)를 공개했다.

인텔은 데이터센터용 차세대 인텔 제온 스케일러블 프로세서인 사파이어 래피즈와 인프라 처리 장치(IPU) 외에도 이번 행사에서 새로운 두 개의 x86 코어 아키텍처와 인텔 쓰레드 디렉터 워크로드 스케줄러를 탑재한 인텔 최초의 퍼포먼스 하이브리드 아키텍처의 앨더레이크, 그래픽 아키텍처 제품군으로 Xe HPG와 Xe HPC 아키텍처, 알케미스트와 폰테배키오 시스템-온-칩(SoC) 등 다양한 기술을 발표했다.

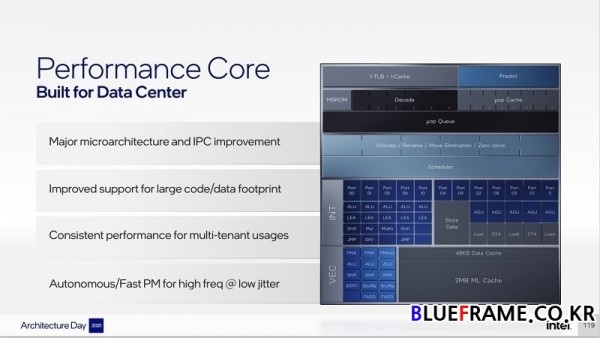

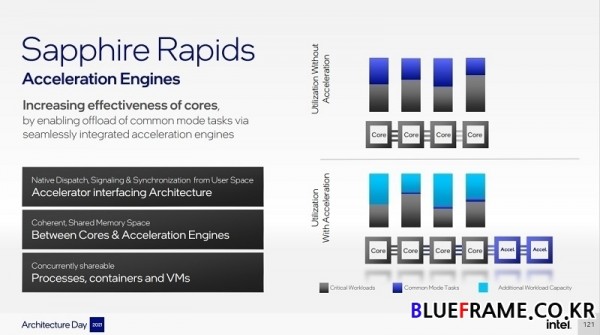

사파이어 래피즈(Sapphire Rapids)는 인텔의 퍼포먼스 코어와 새로운 가속 엔진을 결합한 차세대 데이터센터 프로세서의 표준을 정립했다.

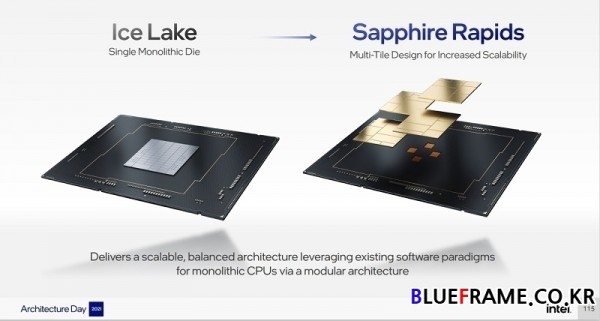

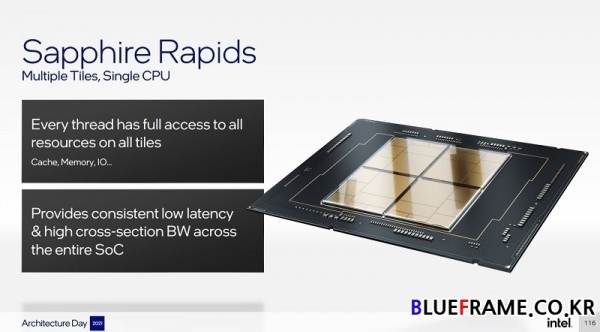

사파이어 래피즈 중심에는 인텔의 EMIB 패키징 기술과 고급 메시 아키텍처 덕분에 단일 CPU 인터페이스의 이점을 유지하면서 상당한 확장성을 제공하는 타일 방식의 모듈식 SoC 아키텍처(Multiple Tiles, Single CPU)가 포함되어 있다.

사파이어 래피즈는 가장 큰 데이터센터 플랫폼 발전을 보여준다. 사파이어 래피즈는 점점 더 까다로워지는 데이터센터 사용 전반에 걸쳐 상당한 컴퓨팅 성능을 제공하며 클라우드, 마이크로서비스 및 AI와 같은 탄력적인 컴퓨팅 모델에서 높은 성능을 제공하도록 워크로드에 최적화되어 있다. 사파이어 래피즈의 중심에는 인텔의 EMIB 패키징 기술을 활용해 상당한 확장성을 제공하면서 동시에 단일 CPU 인터페이스의 이점을 유지하는 타일 방식의 모듈식 시스템-온-칩(SoC) 아키텍처가 포함되어 있다.

인텔 7(Intel 7) 공정 기술을 기반으로 구축되었으며 인텔의 새로운 퍼포먼스-코어 마이크로아키텍처가 적용되어 대기 시간이 짧고 단일 쓰레드 애플리케이션 성능의 한계를 극복한다.

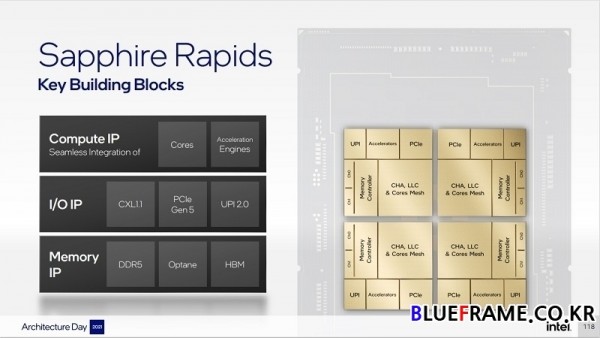

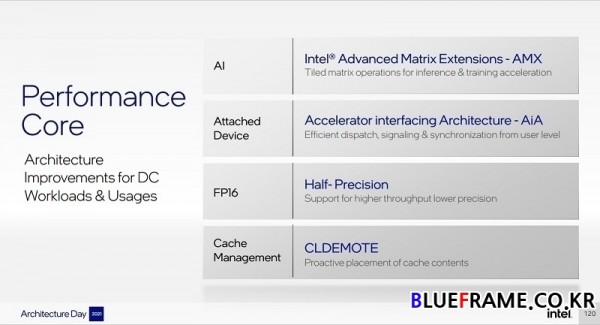

사파이어 래피즈는 새로운 인스트럭션 세트 아키텍처(Instruction Set Architecture) 및 통합 IP를 포함, 업계에서 가장 광범위한 데이터센터 관련 가속기를 제공해 광범위한 고객 워크로드 및 사용에 있어 향상된 성능을 제공한다.

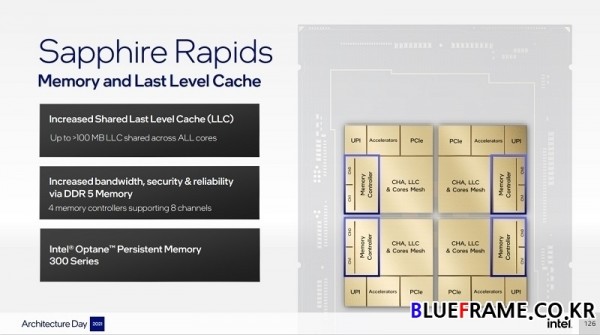

사파이어 래피즈는 균형 잡힌 단일 메모리 엑세스 아키텍처를 제공한다. 모든 쓰레드는 캐시, 메모리 및 입출력(I/O)를 포함한 모든 타일의 리소스에 엑세스할 수 있다. 전체 SoC에서 지연율이 낮고 횡단 대역폭이 높다.

인텔 엑셀러레이터 인터페이싱 아키텍처(AIA)는 가속기 및 장치에 대한 효율적인 전송, 동기화 및 신호 전송을 지원한다. 인텔 어드밴스드 매트릭스 익스텐션(AMX)은 사파이어 래피즈에 도입된 새로운 가속 엔진으로 딥러닝 알고리즘의 핵심인 텐서 프로세싱에도 매우 빠른 속도를 제공한다. 사이클당 2K INT8 및 1K BFP16 연산을 통해 컴퓨팅 기능을 대폭 향상할 수 있다. 초기 사파이어 래피즈 실리콘에서 최적화된 내부 매트릭스-멀티플라이 마이크로벤치마크 구동시 인텔 AVX-512 VNNI 인스트럭션을 활용한 동일한 마이크로 벤치마크 대비 새로운 인텔 AMX 명령어세트를 사용하면 7배 더 빠른 속도를 보인다. 학습과 추론용 AI워크로드 전반에서 상당한 성능 개선을 제공한다.

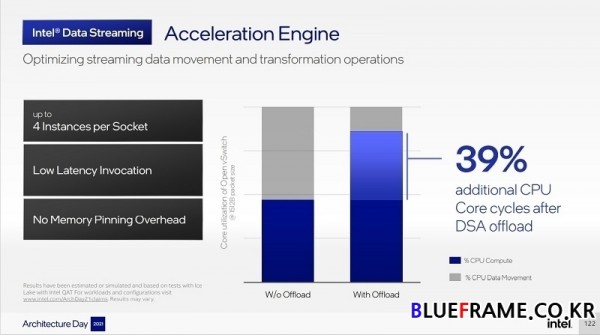

인텔 데이터 스트리밍 가속기(DSA)는 데이터센터 확장 구축에서 발생하는 오버헤드를 유발하는 가장 일반적인 데이터 이동 작업을 오프로드하도록 설계됐다. 인텔 DSA는 이러한 오버헤드 작업 처리를 개선해 전반적인 워크로드 성능을 향상하고, CPU, 메모리 및 캐시뿐 아니라 연결된 모든 메모리, 스토리지, 네트워크 장치 간 데이터를 이동할 수 있다.

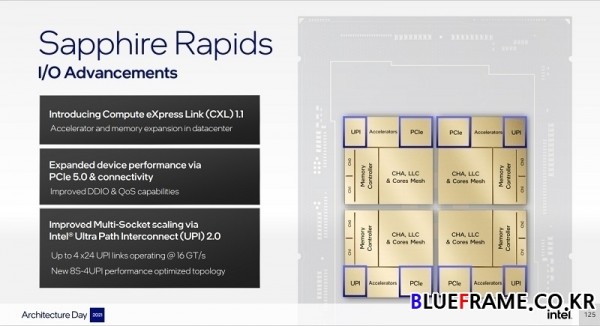

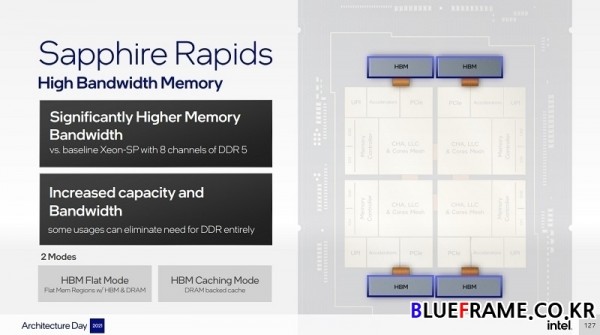

사파이어 래피즈는 클라우드, 데이터센터, 네트워크 및 지능형 엣지에서 가장 광범위한 워크로드 및 구현 모델에 탁월한 성능을 제공한다. 프로세서는 PCIe 5.0, CXL 1.1, DDR5, 및 HBM 기술, 향상된 가상화(Enhanced Virtualization Capabilities) 등을 포함한 첨단 메모리 및 차세대 입출력(I/O)로 업계 기술 전환을 주도하도록 설계됐다.

인프라 처리 장치(IPU)는 클라우드 및 통신 서비스 공급자가 중앙 처리 장치(CPU)의 오버헤드를 줄이고 성능을 높일 수 있도록 설계된 프로그래밍 가능한 네트워킹 장치다.

인텔 IPU 기반 아키텍처는 인프라 기능과 테넌트 워크로드를 분리해 테넌트가 CPU를 완전히 제어할 수 있다. 클라우드 운영자는 인프라 작업을 IPU로 오프로드하여 CPU 활용률 및 수익을 극대화할 수 있다.

IPU는 디스크 없는 서버 아키텍처를 통해 스토리지 용량을 효율적으로 사용하면서 대기 시간을 단축하는 스토리지 트래픽을 관리할 수 있다. 고객은 IPU를 통해 프로세싱과 스토리지의 균형을 유지할 수 있는 안전하고 프로그래밍 가능하며 안정적인 솔루션을 통해 자원을 더 잘 활용할 수 있다.

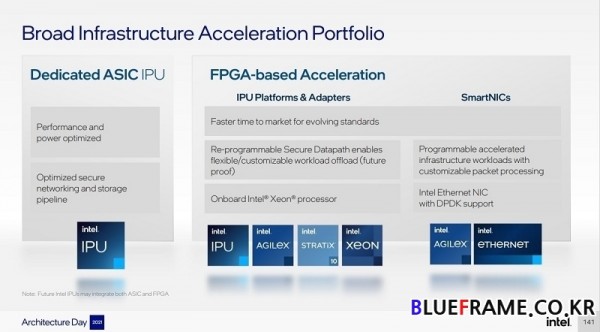

인텔은 “만병통치약은 없다”는 점을 인식하고 있으며 IPU 아키텍처를 보다 심층적으로 살펴보고 다양한 분산 데이터센터의 복잡성을 해결하도록 설계된 새로운 IPU 제품군을 소개했다.

마운트 에반스(Mount Evans)는 인텔 최초의 ASIC IPU로, 최고의 클라우드 서비스 제공업체와 공동으로 설계 및 개발되었으며, 여러 세대의 FPGA 스마트NIC에서 배운 지식을 적용했다. 하이퍼스케일 지원, 고성능 네트워크크 및 스토리지 가상화 오프로드를 제공하는 동시에 높은 수준의 제어 기능 유지, 방화벽 및 가상 라우팅과 같은 사용 사례를 지원하는 동급 최고의 프로그래밍 기능 패킷 처리 엔진 제공, 인텔 옵테인 기술에서 확장해 NVMe 디바이스를 모방하는 하드웨어 가속 NVMe 스토리지 인터페이스를 구현한다.

인텔의 고성능 퀵 어시스트(QuickAssist) 기술을 활용한 고급 암호화 및 압축 가속화 구현, DPDK와 SPDK 및 파이프라인을 비롯한 일반적으로 배포되는 기존 소프트웨어 환경을 사용해 인텔의 베어풋 스위치(Barefoot Switch) 사업부가 개척한 P4 프로그래밍 언어를 사용 가능하다.

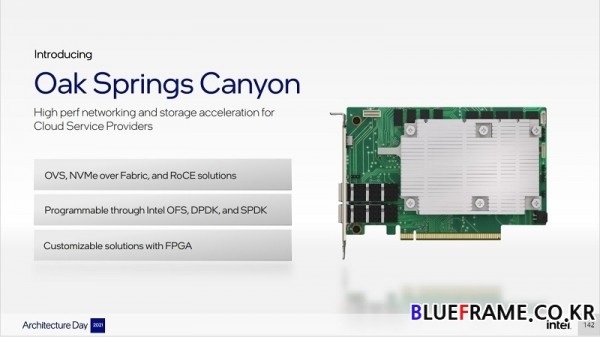

IPU(Infra Processing Unit, 인프라 처리 장치)는 인텔 최초 FPGA 기반 IPU 레퍼런스 플랫폼인 오크 스프링스 캐년(Oak Springs Canyon)과 코드명 마운트 에반스(Mount Evans)라는 인텔의 최초 전용 ASIC 기반 IPU를 공개했다.

오크 스프링스 캐년(Oak Springs Canyon)은 인텔 제온D 및 애질렉스 FPGA로 구축된 IPU 참조 플랫폼으로 전력, 효율성 및 성능 면에서 업계 최고 수준의 성능을 보여준다. 오픈 가상화 스위치(Open Virtual Switch)와 같은 네트워크 가상화 기능과 패브릭 및 RoCE v2를 통한 NVMe와 같은 스토리지 기능을 오프로드하고, 강화된 암호화 블록을 제공해 보다 안전한 고속 2x100Gb 이더넷 네트워크 인터페이스를 제공한다. 확장 가능하고 소스 액세스 가능한 소프트웨어 및 하드웨어 인프라인 인텔 오픈 FPGA 스택을 통해 인텔 파트너와 고객이 솔루션을 최적화된 정의가 가능하도록 지원, X86에 최적화된 DPDK 및 SPDK를 포함함해 일반적으로 배포되는 기존 소프트웨어 환경을 사용해 프로그래밍 가능하다.

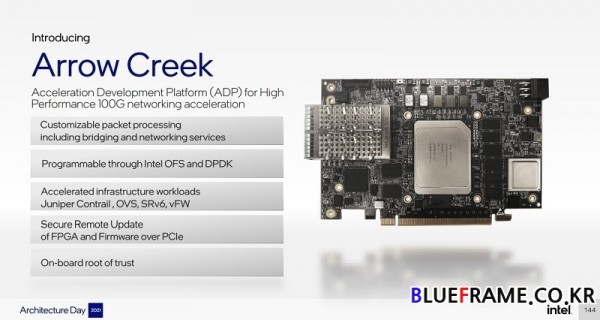

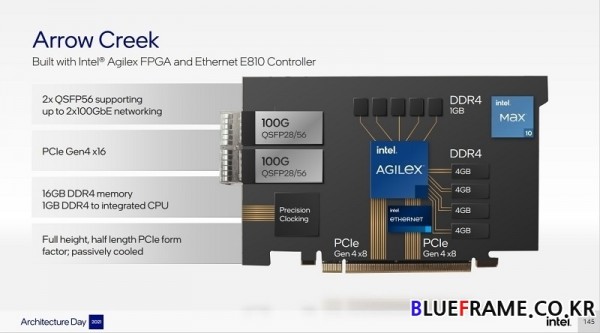

코드명 애로우 크릭(Arrow Creek)인 인텔 N6000 액셀러레이션 개발 플랫폼(Intel N6000 Acceleration Development Platform)은 SmartNIC 제품으로 Xeon 기반 서버와 함께 사용하도록 설계됐다.

인텔 애질렉스 FPGA(Agilex FPGA)는 전력, 효율성, 성능 면에서 업계 최고의 FPGA이다. 고성능 100G 네트워크 가속을 위한 인텔 이더넷 800 시리즈 컨트롤러. 통신사업자가 주니퍼 콘트레일(Juniper Contrail), OVS, SRv6와 같은 유연한 가속 워크로드를 제공할 수 있도록 하는 여러 인프라 워크로드를 지원한다. 인텔의 PAC-N3000의 성공에 기반하고 있으며 세계 최고 통신사업자는 이미 이러한 워크로드를 구축했다.

인텔, intel, 차세대, 제온 스케일러블 프로세서, Xeon Scalable Processor, 데이터센터 프로세서, 표준 정립, 퍼포먼스 코어, 새로운, 가속 엔진, 결합, 인텔 7, Intel 7, 인프라 처리 장치, IPU, 발표, 공개